### New Release

### **LTEC Corporation**

Your most experienced partner in IP protection

## INFINEON HALF BRDGE MODULE(FF11MR12W1M1\_B11) 1200V CooLSiC ™ MOSFET ANALYSIS REPORT

**Sep 2017.** LTEC Corporation released a detailed structure and process analysis report of 1200V 1200V CooLSiC TM MOSFET device. This devise is the 1<sup>st</sup> product from Infeneon using unique asymmetric trench gate transistor. This device has low Ron comparable with other device makers such as Rohm, Wolfspeed.

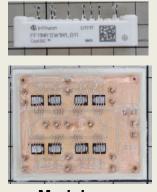

Module

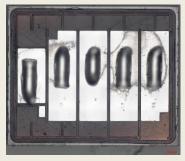

SiC die

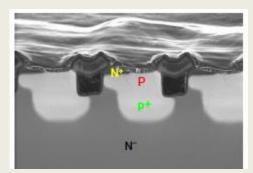

**SEM** cross section

#### **Device features**

- Max. operating voltage: 1200V, rated DC Drain current ID @25°C = 100A

- Very low specific On-resistance, RON x A=  $36m\Omega$  x mm<sup>2</sup>

The report has two individually purchasable sections: a Structure Analysis (80pages) and a Process Analysis section (29pages). The Structure Analysis section reveals the physical construction of the device, including EDX materials analysis, and many other fine details. The Process Analysis section includes manufacturing process flow, the estimated number of photomasking steps, and the impurity concentration of the epitaxial layer.

Structure analysis report: \$5,000 Process analysis report: \$4,000

**Contact LTEC Corporation**

info@ltecusa.com

## **Table of Contents Structure Analysis Report**

|                                                            | Page |

|------------------------------------------------------------|------|

| Device summary, Table 1, Executive Summary                 | 3    |

| Analysis results                                           | 4    |

| Table 2. Module structure overview                         | 5    |

| Table 3. Device structure: SiC MOSFET                      | 6    |

| Table 4. Device structure: Layer materials and thicknesses | 7    |

| Module overview                                            | 8    |

| Electrical characteristic measurement                      | 13   |

| SiC MOSFET Analysis                                        | 19   |

| Plain view (Optical Microscope)                            | 20   |

| Plain view, Scanning Electron Microscope (SEM)             | 29   |

| Cross-sectional structure analysis (SEM)                   | 36   |

| Module structure analysis                                  | 48   |

| EDX material analysis                                      | 60   |

# **Table of Contents Process Analysis Report**

|                                                                     | Page |

|---------------------------------------------------------------------|------|

| Analysis summary                                                    | 3    |

| Comparison summary (Infineon, Wolfspeed, Rohm)                      | 4    |

| Die                                                                 | 5    |

| Die edge                                                            | 5    |

| Device structure SiC MOS FET                                        | 7    |

| Transistor schematic diagram                                        |      |

| SiC MOSFET cell                                                     |      |

| Plain view                                                          | 11   |

| (a) Die schematic diagram                                           |      |

| (b) Layout pattern schematic diagram                                |      |

| SiC MOS FET front-end wafer process flow (estimated)                | 16   |

| SiC JFET process sequence cross-sectional view                      | 18   |

| Relationship between device structure and electrical characteristic | 20   |

| Appendix                                                            | 28   |

| Relevant references                                                 |      |

| Relevant patents                                                    |      |